2D 및 3D 구조의 실리콘 및 패키징 집적기술 늘어나

차세대 SOP 기술개발 노력 中

반도체 진보를 위해 전기적, 열적 및 I/O 스케일링의 기술 로드맵 요구에 확대가능하게 한다. 지속적인 연구와 향상은 언급된 데이터베이스, 실리콘 패키지 제조, 테스트 및 어셈블리를 포함한 우수한 제조 프로세스를 정의하는데 도움을 줄 것이다. 또한 좀 더 효율적인 비용의 제품 공급을 보이는 제품 애플리케이션에 기술이 직접적으로 도움을 줄 것이다. SOP 테크놀로지에서의 향후 작업에서는 실리콘 관통-비아 컨덕터의 평가, 구조의 전기적 특성, 광-전기 특성 그리고 기계적 및 신뢰성 평가를 포함할 것이다. 또한 향후 작업에서는 첨단 3-차원 구조를 위한 수동부품과 능동IC를 포함할 것이다. 새로운 2D 및 3D 구조를 사용하는 실리콘 및 패키징 집적은 지원 시스템 요구와 새로운 대량 생산 애플리케이션에 흥미를 유발하고 있다.

수동 및 능동 회로 테크놀로지의 집적화

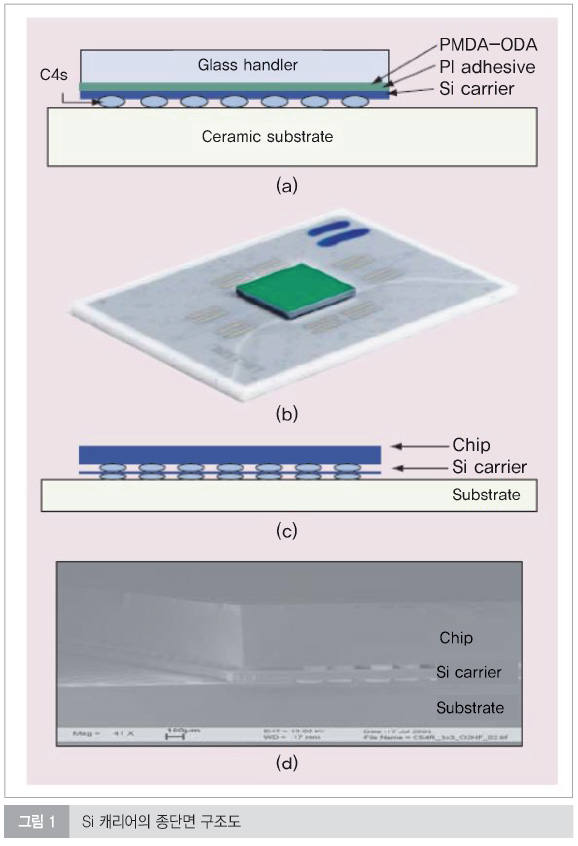

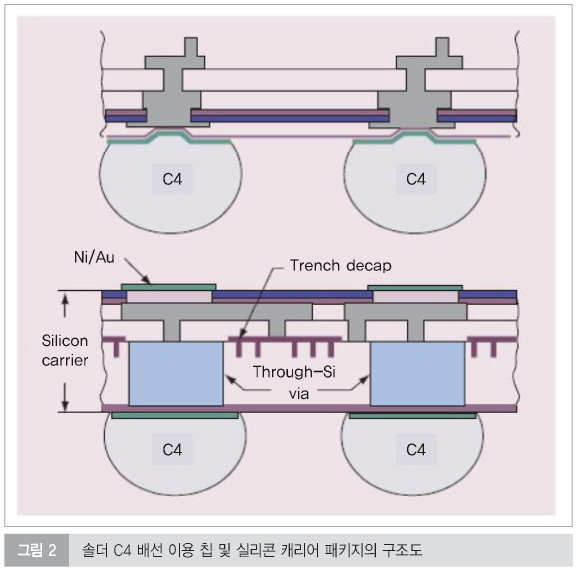

실리콘 캐리어의 유효 표면은 고밀도 톱-다이 배선 와이어링에 이용될 수 있다. 그리고 또한 애플리케이션 디자인에 의존하는 로컬 통합 수동 부품 및 능동 회로 테크놀로지를 지원할 수 있도록 한다. 이러한 콘셉트를 증명하기 위해, 수동-테크놀로지 테스트 평가제품을 만들었다. 여기에서, 전형적인 세라믹 모듈 위의 플립칩 구조가 다이와 기판 사이에 디커플링 커패시턴스(decap)가 통합된 실리콘 캐리어의 삽입물로 어셈블리됐다.

디커플링 커패시턴스가 통합된 실리콘 캐리어는 2.5㎌/㎠ 디커플링 커패시턴스 보다 더 높게 측정되었다. 칩 그라운드 및 전압 접속은 실리콘 캐리어부터 칩까지 만들어지고, 이번 테스트 시제품에 사용된 트렌치 기반 커패시터 어레이 가장 자리에 접속된다(그림 1 및 그림 2 참조). 하드웨어 모델링과 특성 결과는 고주파 혹은 중간 주파수 애플리케이션에서 노이즈를 억제하기 위해 기회가 존재하고 있음을 나타내고 있다.

칩 및 패키지 레벨 통합

실리콘 웨이퍼가 1) 200~300+㎛ 웨이퍼 두께의 self-supporting, 2) 10㎛ 이하 웨이퍼 두께의 기계적 지지 형태로 프로세스되어 왔기 때문에, 웨이퍼는 절삭, 세척, 본딩 공정을 지난다.

뿐만 아니라 스택 혹은 Si 캐리어 박막 구조의 기계적 지지 구조 제거도 진행된다. 가공된 구조에 의존하는 μ-C4는 또한 인접한 구조에 접합을 위한 웨이퍼 레벨에서 차후 공정을 통과하여 절삭 이전에 추가될 수도 있다. Self-supporting 웨이퍼는 표준 웨이퍼-절삭 작업을 이용해 절삭될 수 있다. 그래서 이들 구조는 칩과 비슷하게 취급될 수 있고, 화학 세척 및 본딩을 견딜 수 있다.

기계적인 지지대 구조는 웨이퍼 관통하면서 그리고 일부분 혹은 전 부분이든 기계적지지 구조를 통과하면서 식각되거나 절삭된다. 후자의 경우를 예를 들면, 실리콘 캐리어 구조는 유기 혹은 세라믹 캐리어 지지를 위해 가공 및 접합되어 왔다. 그리고 기계적 지지대는 레이저 방출 및 화학/열 세척을 포함한 공정들이 조합되어 제거되어 왔다. 칩 스택 구조의 경우, 기계적으로 지탱된 웨이퍼는 인접한 웨이퍼와 결합되거나 혹은 박막 웨이퍼 다이-스택 구조가 기계적 지지대 구조 및 그 다음의 세척의 제거로 이어질 수 있다. 열 혹은 레이저 방출 프로세스는 기계적 지지대 구조 해체를 위해 이용될 수도 있다. 아래에서 IBM 레이저 방출 공정을 자세하게 설명했다.

비가시적인 펄스 UV 레이저 혹은 방출 공정용 IR 레이저의 선택은 무엇보다 다량의 펄스 및 감응력 그리고 기판에 대한 확실한 열 데미지 손실에 의한 식각 폭 컨트롤을 위한 전자의 성능 때문이다. 전형적인 UV 레이저 펄스 폭은 대략 450mJ 레이저 에너지의 약 20~30ns이다. 샘플 표면에서의 빔 사이즈는 거의 0.5~1.5㎠이 될 수도 있다. 결과적으로, 어떠한 손실도 경험하지 않았다면 레이저 광학 때문에 감응력 범위는 900mJ/㎠~300mJ/㎠이다.

PMDA-ODA 폴리이미드(PI) 레이저 절삭임계(laser ablation threshold)는 약 50mJ/㎠이다. 이는 심지어 절삭임계 이하의 감응력을 지닌 큰 스트레스 펄스가 구조에 일반화되었다는 것을 알 수 있다. 이는 절삭을 위한 임계치 이하에서 매우 중요한 ~10mJ/㎠ 감응에 노출되었을 때, ~104Pa 스트레스 펄스가 PMDA-ODA PI 필름에서 나타났음이 보고되어 왔다. 그러나 Doany 및 Narayan은 100mJ/㎠에 육박한 감응력 사용이 심지어 PI 두께가 3㎛일 때도 금속-폴리머 박막 와이어링 구조에 피해를 유발하지 않는다고 밝혔다.

실리콘 캐리어 애플리케이션에서 핸들러 웨이퍼 제어 중 하나의 예는 C4-본드된 상태의 단일화되어 발생한다. 그림 8의 (a)에서 종단면 구조를 보여주고 있다. 기판 결합 및 칩-투-실리콘 캐리어 결합으로 단일화된 Si 캐리어의 실험이 발전되고 있다. 실리콘 캐리어-투-기판 피치 어셈블리는 200㎛이고, 칩-투-실리콘 캐리어 결합은 양쪽 모두 100㎛과 50㎛으로 향상되었다. 기판에 실리콘 캐리어의 어테치 직후에 관해 앞서 설명한 바와 같이, 릴리즈 및 캐리어 표면(핸들러에 어테치되는)의 클리닝은 특정 폴리머 잔사를 제거함으로써 완성됐다. I/O 패드가 세척되고, 파인-피치 I/O 칩이 그림 1에서 보는 바와 같이 Si 캐리어 표면에 접합되었다.

전기 성능 특성

Si 캐리어에서 시그널 배선을 위한 두 개의 메인 블록 수립 방법은 수평적인 와이어링과 수직적인 관통전극이다. 이들 부품의 전기 성능은 전형적으로 시간과 주파수 영역 모두에서 특성화된다. 중·저급의 데이터 률 애플리케이션에서는 시간 영역이 강조되고, 하이-엔드 데이터 률 애플리케이션에서는 주파수 영역이 좀 더 강조된다. 다음 부분에서 전형적인 특성의 예들이 이들 Si 캐리어 부품의 전기 성능 잠재성을 보여주고 있다.

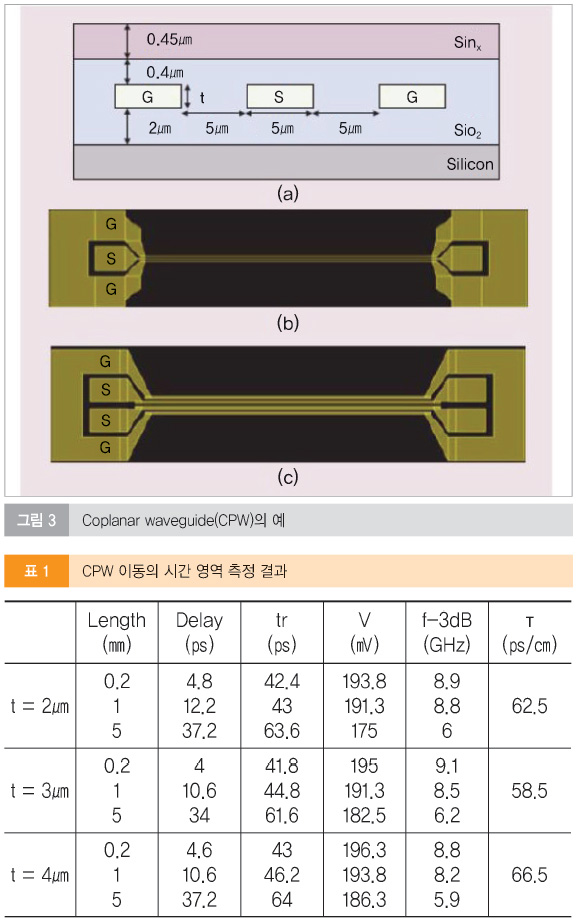

중·저 데이터 률의 애플리케이션용 평행 도파관(CPW)(≤10Gb/s)

실리콘 캐리어 기술을 이용함으로써, 예를 들어 전자광학 트랜시버(EOT, electro-optic transceiver) 혹은 MMCM의 첫 번째 예(그림 3 참조. GSG(ground-signal-ground)와 GSSG(ground-signal-signal-ground)의 것으로 (a) 종단면, (b)와 (c)는 위에서 본 모습이다)이며, 상대적으로 단 펄스 전파를 이용한 시간 영역으로 특색지어지는 CPW(co-planar waveguides)로 구성된다. 입력 소스 펄스는 197.5㎷ 진폭과 39.8㎰ 상승시간을 가지고 있다. 첫 번째 예에서, 라인 끝자락의 출력 펄스가 기록되어지고 입력 펄스와 비교되어 있다. 동박 컨덕터 두께는 2, 3, 4㎛ 라인 길이는 0.25, 1, 5㎜ 라인 길이로 다양했다.

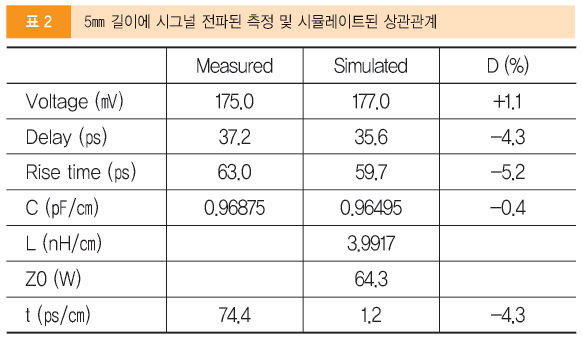

표 1에서는 전파된 시그널, 전파된 상승시간, tr의 50% 레벨에서 추출된 지연 평가를 보여주고 있다. 또한 10%와 90% 레벨 사이의 시그널 진폭, -3dB 전파 포인트 및 유닛 길이당 전파 지연 등을 보여주고 있다.

배선 대역폭은 다음과 같이 정의된다.

하나는 fc=1/2πRC의 ‘3dB 상부’ 주파수를 가지고 있는 저역 통과기(low-pass filter)로써 작동을 위한 배선을 고려할 수 있다. ‘RC’ 개념과 같은 경우, tr=2.2 RC=0.35fc이다. 일그러지지 않은 전파를 유지하기 위해서, 임계 주파수 fc는 데이터-비트 혹은 사이클 타임도 뜻하는 펄스 폭(pw)의 역순과 동일하게 되어야만 한다. 이는 tr,0.35pw를 의미한다. 볼 수 있듯이, 거의 8.5GHz의 대역폭은 1㎜ 긴 라인 그리고 거의 6.0GHz의 대역폭은 5㎜ 긴 라인을 이뤄질 수 있다. 이는 짧은 라인 길이를 넘어 Gb/s 데이터 률 지원에 대응한다.

컨덕터 두께가 2㎛~3㎛까지 다양할 때 약간의 대역폭 향상이 나타났다. 비록 2㎛ 두께 라인이 22.3Ω/㎝의 저항을 지녔다고 할지라도, 4㎛ 라인보다 2.3배 더 큰 5㎜의 긴 라인이 실제로 낮다(5.9GHz vs 6GHz). 이는 측정된 커패시턴스가 4㎛ 굵은 선(1.4㎊/㎝ vs 0.97㎊/㎝) 보다 41% 정도 실제로 높기 때문이다. 3㎛ 굵은 라인은 6.2GHz의 약간 더 큰 대역폭을 가지고 있다.

2, 3, 4㎛ 금속 두께 및 5㎛ 폭의 경우에 라인 커패시턴스 값은 각각 0.97, 1.05 그리고 1.37㎊/㎝이고, 라인 저항은 22.3, 13.8 그리고 9.65Ω/㎝이다. 이러한 라인들은 혼합 실리콘 캐리어 구조 제조의 첫 번째 시도였다. 향후 테스트 사이트에서는 종단면(절연체 높이에 달하는 높이의 폭)을 최적화시킬 것이다. 4㎛ 넓이 라인으로 진행될 때의 침식은 유닛 길이당 라인 커패시턴스(유닛 길이당 저항의 감소보다 더 크다)가 증가하기 때문이다. 그래서 지연 및 상승 시간 전파가 늘어난다. 5㎛ 넓은 라인이 또한 종단했다. 라인 너비가 4.9㎛이고, 공간은 5.1㎛이며, 두께는 2.8㎛이고, 실리콘 위의 높이는 2.0㎛이다. 라인 위의 얇은 질화 레이어는 7개의 절연체로 구성된 0.63㎛ 두께를 지녔다. 이들의 치수 및 22.4Ω/㎝의 유닛 길이당 측정된 저항을 기본으로, 금속 저항력은 1.95μΩ/㎝로 나타났다. 축적된 커패시턴스는 Ccal = 0.96㎊/㎝이며, 반면, 측정된 값은 Cmeas = 0.97㎊/㎝ 혹은 단지 0.4% 차이가 난다. 그래서 이들 재질 파라미터는 IBM에서 개발한 CZ2D(모멘트 법의 전자기 분야의 해결책)를 이용한 유닛 길이당 주파수-종속 R(f)L(f)CG 파라미터를 지닌 전송-라인 모델을 얻기 위해서 사용되곤 한다. IBM의 PowerSpice 회로 시뮬레이터는 5㎜ 긴 라인 사이에서 시그널 전파 시뮬레이트를 위해 사용되었다. 소스는 TDT 측정기 상에서 나타난 동일한 197.5㎷ 진폭과 39.8ps 상승 시간을 가지고 있다. 소스 임피던스와 터미네이션 모두는 50Ω이었다. 표 2에서는 측정된 것과 시뮬레이션 한 결과를 잘 보여주고 있다.

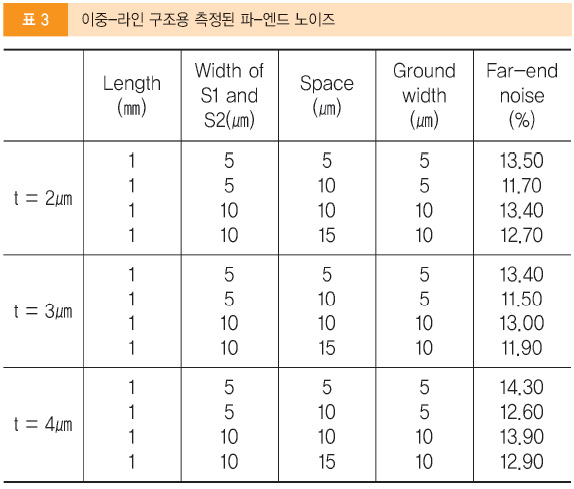

커플링 효과는 또한 그라운드-시그널-시그널-그라운드 구조에서 1㎜로 고정된 라인 길이의 비슷한 치수의 라인 사이를 연구되었다. 너비, 두께 및 컨덕터의 공간은 측정된 far-end 노이즈와 함께 표 3에 나열했다. 이 경우, 단지 스텝 소스와 측정된 라인 엔드는 50Ω인 반면 액티브-라인 엔드 및 니어-엔드 콰이어트-라인 엔드는 오픈-엔드이다. 만약 모든 엔드가 제거된다면, Cross-talk는 표 2에 나열된 것과 같이 절반의 진폭이 되었다. 측정된 far-end 노이즈는 14% 미만이고, 11.5% 정도로 낮아질 수 있다. -3dB 주파수와 비교해 보면, 동일한 2㎛ 두께와 비교해 더 좋은 성능을 지닌 3㎛ 두께로 된 라인과 비슷한 양상을 보였다. 라인 두께가 4㎛로 더 늘어날 때 성능이 줄어들기 시작된다.

전체적으로, 크로스토크는 패키지 배선에서의 변수 발생과 비슷하고, 온-칩 와이어링보다 더욱 낮다. 그래서 실리콘 캐리어는 저손실의 온-칩 와이어링의 대역폭을 확장할 수 있다. 그리고 또한 레벨에서 보여준 낮은 노이즈를 지닌 고밀도 와이어링을 제공할 수 있다.

고속 데이터 애플리케이션용 차원 다른 마이크로스트립(≥10Gb/s)

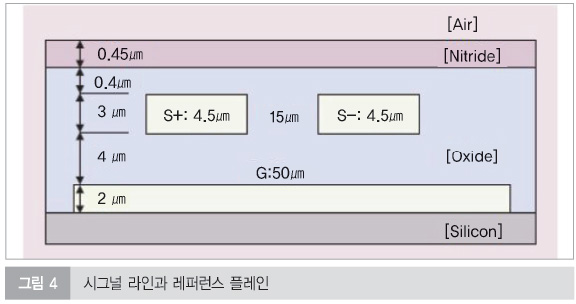

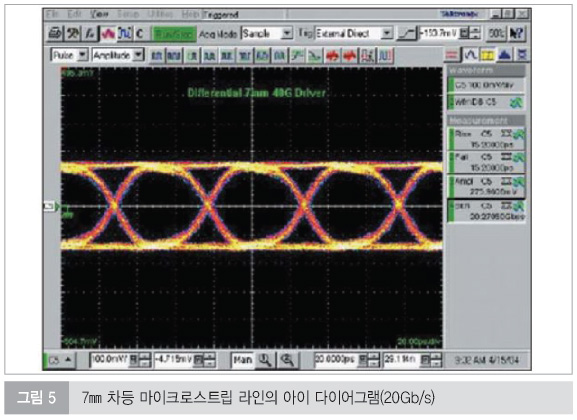

다음의 예에서는 그림 4에서 보는 바와 같이 고속 데이터 전송비율 애플리케이션(10Gb/s 이상)용의 차원이 다른 마이크로스트립 라인을 포함하고 있다. CPW(co-planar waveguide) 구조와 대조적으로 시그널 컨덕터는 로시 실리콘 기판(lossy silicon substrate)을 대비하기 위해 실드로 처리되어서 전체 감쇠(overall attenuation)를 감소한다. CPW이 싱글-엔드가 아니라 임피던스 제어가 되는 동안 라인은 100±10Ω 차동 임피던스(differential impedance)를 충족시키도록 설계되었다. 이 결과가 대역폭에서 상당한 이득을 발생할 것을 볼 수 있을 것이다. 테스트 구조는 라인 길이 범위가 0.5㎜~0.7㎜까지 보였다. 마이크로스트립은 GSSG(ground-signal-signal-ground) 마이크로프로브를 이용해서 접촉된다. 아이 다이어그램(Eye diagram) 측정은 라인이 몇 ㎜ 이상의 20Gb/s 데이터를 전송할 수 있는지를 보여주고 있다. 예를 들어, 그림 5에서는 20Gb/s에서 7㎜ 마이크로스트립 길이가 아이 오프닝에 적용될 수 있음을 볼 수 있다.

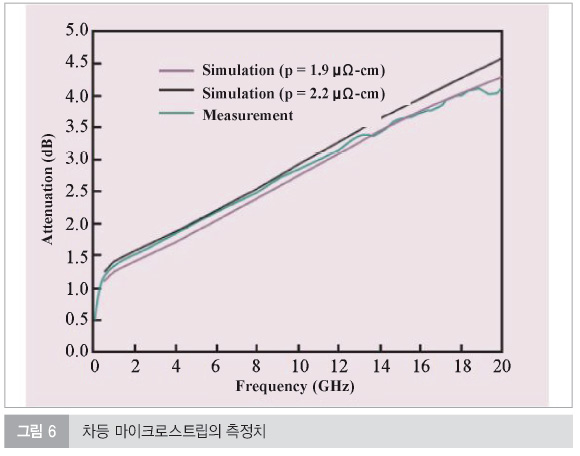

주파수 도메인 측정은 캘리브레이션 기판과 SOLT(short-open-load-through) 기술 레퍼런스를 이용한 프로브 팁을 조정한 벡터 네트워크 분석기를 이용해 이뤄졌다. 감쇄는 서로 다른 길이 마이크로스트립 라인의 직렬 T-파라미터의 고유값 분석을 이용한 S-파라미터(그림 6 참조)로부터 얻었다. 이는 7㎜ 20GHz에서 총 감쇄가 약 3dB라는 결론을 내릴 수 있다; 즉, 이 라인 길이에서 대역폭이 20GHz이다. 이는 단지 5㎜ 길이 CPW를 이를 수 있는 6GHz 대역폭 이상이다. 보는 바와 같이, 시뮬레이션 일치는 금속의 저항성은 지적된 범위 내에서 다양할 수 있다는 사실이 매우 잘 고려되었다. 시뮬레이션된 파라미터 보고서에 따르면, 감쇄가 컨덕터 손실에 의해 완벽하게 좌우된다는 것이 발견되었다. 산화 내의 손실들은 무시할 수준이다. 또한 실리콘의 존재는 그라운드 플레인으로 충분하게 실드되는 역할을 하지 못한다.

시뮬레이션에서 보면, 차등 특성의 임피던스는 약 40GHz에서 105Ω로 결정된다. 이는 보통 ±10% 마진을 가진 100Ω 디자인 포인트의 경우 매우 충분하다. 그러나 이는 라인이 극도로 매우 좁다는 것과 넓은 라인(즉, 4.5㎛ 대신의 5㎛)이 좀 더 적합해질 수도 있음을 보인다. 라인 폭 내에서의 증가는 임피던스와 감쇄를 동시에 낮춘다. 전체적으로, 이는 차등 마이크로스트립 구조를 이용해 몇 ㎜ 이상 고속 데이터 전송비율(10Gb/s 이상)이 쉽게 달성될 수 있다는 것이 명시되기 시작했다.

관통전극 인덕턴스

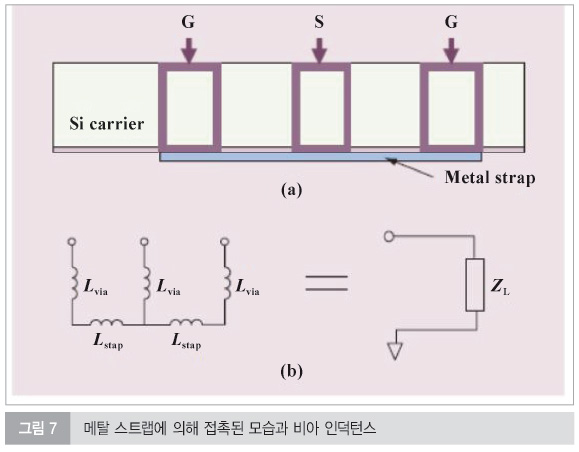

마지막 예제(그림 7참조)는 2개의 반환 비아(G)에 하단부에서 시그널 라인으로 묶임으로써, 중앙 비아(S)를 지닌 3개의 비아로 구성되어 있다. 총 비아 직경은 70㎛이고, 비아 피치는 100㎛이었다. 185㎛ 및 271㎛ 두께를 지닌 두 개의 웨이퍼는 GSG(ground-signal-ground) 사이트에서 측정되었다. 사이트는 625㎛의 500㎛ 혹은 625㎛ 스트랩의 200㎛으로 뒷면에 묶였다. 구조는 GSG 마이크로프로브를 가지고 프로브되었다. 그리고 레퍼런스 기판에 SOL(short-open-load) 캘리브레이션 한 후에 반사 계수는 45MHz~40GHz까지 벡터 네트워크 분석기를 가지고 측정되었다. 그런 후에 비아 인덕턴스(Lvia)는 다음과 같은 방법을 이용해 반사 데이터로부터 추출되었다. 입력 임피던스는 Ω=2πf인 곳에서 ZL = R + j(i)Ltotal로 추정된다. 반사는 입력 임피던스로 전환되면 될수록, 가상의 부분과 총 임피던스(Ltotal)는 적합한 경사가 얻을 수 있다. 측정용 단순하게 동등한 회로와 비아 인덕턴스 추출은 그림 7에 보여주고 있다. 이 단순한 접근법은 거의 30GHz에 근접하는 우수한 적합을 일반적으로 제공한다.

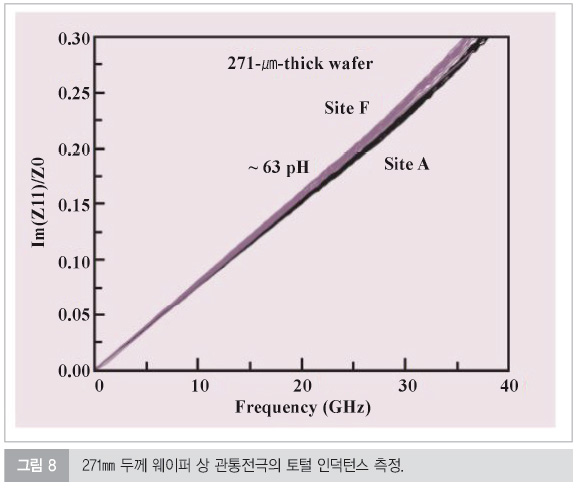

싱글 비아의 값은 내려온 싱글 비아의 합계와 평행 상에서 두 개의 반환 비아의 합계인 총 임피던스(즉, 스트랩의 조력 및 상호 인덕턴스가 무시된)를 추정함으로써 최종적으로 판명된다: Ltotal = Lvia + 1/2Lvia, 이후 Lvia = 2/3Ltotal이다. 차등 두께의 두 개의 웨이퍼에서 여러 위치를 측정했다. 총 인덕턴스를 위한 각각의 웨이퍼가 측정된 값은 그림 8에서 보여주고 있다. 곡선 사이의 미세한 퍼짐은 띠 크기(더 큰 띠 크기는 더 낮은 총 인덕턴스와 관련이 있다) 때문이다. 퍼짐은 비아 인덕턴스 축출에서 Lstrap 항목을 무시할 정도로 충분하다.

결론적으로, 특별한 직경 및 피치의 싱글 비아 인덕턴스에 거의 0.15pH/㎛ 결과를 초래하는 27pH 및 42pH의 값은 185㎛ 두께 웨이퍼와 271㎛ 두께 웨이퍼용에서 각각 발견되었다. 이들 값은 이전 작업보다 더 잘 비교되었다. 일부 연구자는 170㎛ 두께 웨이퍼용 혹은 협소해진 비아(16㎛ 직경)의 0.63pH/㎛용으로 107pH를 제시했다. 이러한 비교적 낮은 관통전극 인덕턴스들은 적은 왜곡 시그널 상호접합과 낮은 인덕턴스 파워-전송 네트워크에 중요하다.

전기적 특성 결론

본 섹션에서는 CPW, 차등 마이크로스트립 및 관통전극의 전기적 특성을 보여주고 있다. 이는 1㎜ 길어진 CPW가 9GHz 대역폭(낮은 혹은 중간 등급의 데이터 비율 애플리케이션에 적용되는)을 지지하지만, 반면 차등 마이크로스트립이 7㎜ 이상의 20GHz 대역폭(고속 데이터 비율 애플리케이션에 적합한)을 이룬다는 것을 지적하고 있다. 칩 위에서보다 이러한 배선이 낮은 저항손실(resistive losses) 및 더 낮은 크로스토크이기 때문에 실리콘 캐리어는 BEOL 와이어링보다 더 높은 대역폭을 제공할 수 있다. 하지만, 어떠한 거대한 등급도 없는 크로스토크를 지닌 패키지 배선보다 고밀도 와이어링을 제공한다. 관통전극의 주파수 영역 측정은 실행되었고, 100㎛ 피치용 0.15pH/㎛의 효과적인 비아 인덕턴스는 간단한 등가 회로모델을 이용해 축출되었다. 이 낮은 인덕턴스는 저-왜곡 시그널 배선 및 저-인덕턴스 전원-전달 네트워크에 중요하다.

열기계 모델링, 시뮬레이션 및 특성

열기계적 전문

멀티칩 패치지 내부의 열 및 기계적 스트레스 분포는 SOP 모듈의 설계 및 테스트에 있어서 중요한 역할을 한다. 통상적으로는 성분 재료(실리콘 및 실리콘 캐리어 같은)의 CTE 값이 잘 매치된다면, 열 기계 스트레스가 상대적으로 줄어든다고 알고 있다. 이는 사실이다. 그러나 주의사항으로 꼽자면, 강력하게 비균등한 공간 전력 밀도(Q(x, y))에 핫 스폿이 일반화되는 실리콘 칩 내의 상승하는 전력 소실 또한 주어져야만 한다. 그래서 스트레스의 타당도는 일시적이거나 동작 내의 핫 스폿이 원인이 되고, 파워-온 및 파워-오프는 제거되어야만 한다. SOP의 중요 요소로 여겨지는 기계적 스트레스에서 지속적 및 일시적인 온도의 영향은 그래서 성공적인 디자인에 고려되고 있다. SOP 애플리케이션과 관련해서, SOP 모듈, μ-C4, 관통전극 등의 세 개의 항목이 고려되고 있다.

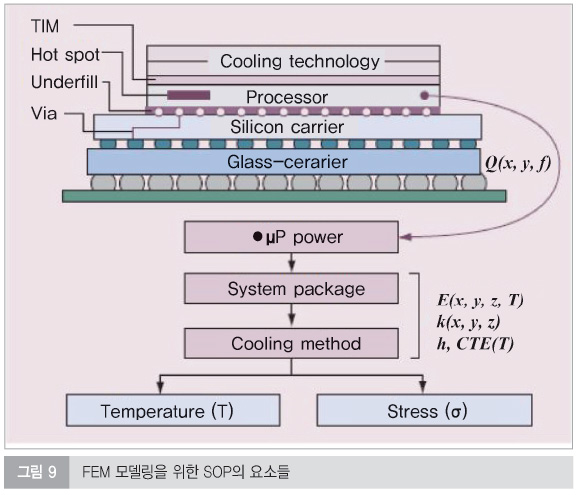

그림 9에서는 싱글 프로세서 SOP 모듈의 종단면을 보여주고 있다. 프로세서에서 소산된 일시적인 전력은 Q(x, y, t)로 표시된다. 실리콘 캐리어뿐만 아니라 수동 칩 내부의 전기 회로가 임베디드된 전력은 쿨링 디바이스에 의해 정기적으로 제거된다. SOP는 싱글 실리콘 캐리어에 놓인 여러 개의 실리콘-기반 칩이 사실상 구성될 수도 있다. 예를 들어 프로세서들, 메모리 스택들 및 스위치로 구성될 수 있다. 칩들은 μ-C4의 빽빽하게 패키지된 어레이를 통해 박막 실리콘 캐리어(예를 들어, 300㎛ 혹은 100㎛ 두께 미만)에 어테치된다. 그래서 프로세서 간의 커뮤니케이션은 μ-C4 및 비아에 따라 접촉한 멀티레이어 금속화를 통해 발생한다.

각각의 칩에서 평균 전력 소산은 추가적으로 핫 스폿에 고려된다. 게다가 전력 평균, 프로세서는 평균보다 5배 더 큰 전력 밀도를 지닌 핫 스폿을 포함할 수 있다.

SOP 모듈

FEM 수립 목표는 전력 분배(Q(x, y, t))를 조건으로 할 때, SOP 모듈 내부에서 온도(T), 스트레스(σ)를 측정하는 것이다. 더욱 큰 목표는 SOP 내부에서 가장 유력한 최대 스트레스인지를 결정되도록 하는 것이다. 이는 유사한 재료의 실패한 스트레스를 초과할 수 있다. 재료의 물리적 특성과 바운더리 조건은 모듈 내에서 온도와 스트레스를 결정한다. 다양한 바운더리 조건들은 시스템에서 증진된다. 예를 들어 쿨링 디바이스는 필름 열전달계수(h)로 정의된 대류 플럭스를 제공하는 반면, 글래스-세라믹의 C4 면은 전도 제한 반도체 절연체를 제공한다. FEM 모델은 심각한 복합성 없이 예상된 모든 시나리오 효과를 얻을 수 있도록 구성되어야만 한다.

μ-C4 내의 스트레스와 기계적 테스트

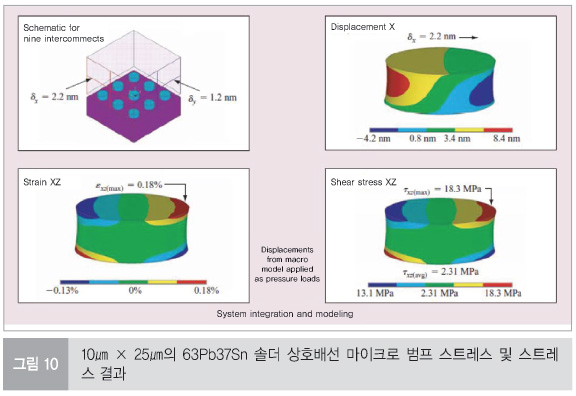

μ-C4 내의 스트레스와 스트레인 레벨의 이해를 높이기 위해 모델의 초창기 발전은 매크로-마이크로 모델의 사용으로 시작됐다. 제한된 요소 모델의 경우, 구조의 매크로 특성은 고려될 수 있다. 반면 각 소형 특징의 높은 체적을 상세하게 이해하는 마이크로-레벨을 여전히 제공하는 것은 기계적 특성의 이해가 필요하다. 예를 들면, 개별적인 μ-C4 레벨 상의 실제 스트레스와 스트레인의 이해를 높이는 동안 모델은 구조 내에서 사용된 대다수의 마이크로접합을 설명한다. 그림 10에서는 X 변위의 예를 지닌 매크로 모델이 XZ 내에서의 스트레인과 XZ 내의 절단 스트레스를 보여주기 위한 μ-C4 레벨에서 생성되는 것을 보여주고 있다. 매크로 모델 내에서 상대적인 압력 적재의 이러한 방법은 상대 비교를 위한 솔더 배선을 구분해줄 수 있다.

μ-C4 내 스트레스의 매크로 및 마이크로-기계 모델링은 다양한 BLM 및 솔더 배선을 통해서 향상될 수 있다.

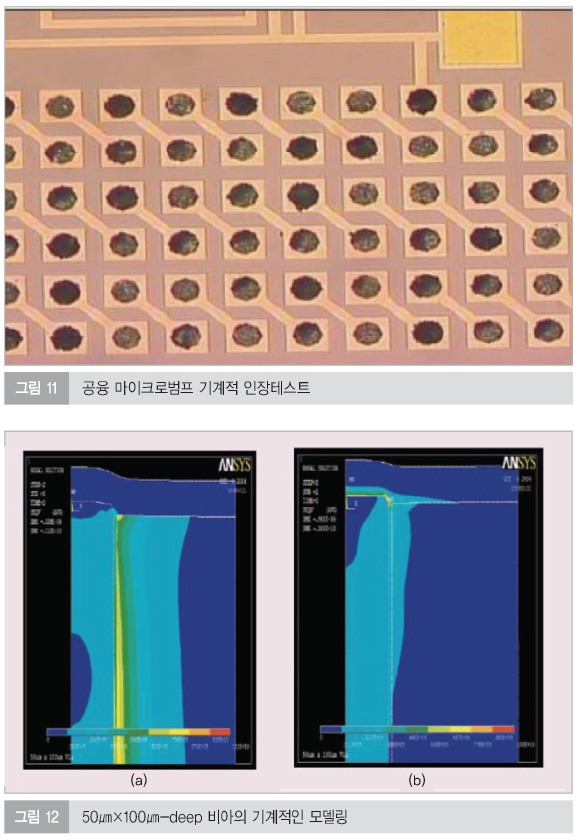

기계적 모델과 실제 샘플 기계적 테스트의 비교는 기계적 인장 및 절단 테스트를 실시함으로써 타깃으로 하는 애플리케이션의 최적화 구조와 관련이 있다. 인장 테스트 결과는 잘못된 모드를 더 잘 이해할 수 있게 한다. 그림 11에서는 솔더에서 100% 실패를 보여주는 공융 솔더 μ-C4의 기계적 인장 테스트를 실시한 구조를 예로 보여주고 있다.

관통-비아

비아와 ILD(inter-level dielectric) 레벨의 제조 프로세싱 동안의 비아 구조의 차동 열팽창은 비아 디자인에서 중요한 이슈이다. 이 문제는 ANSYS 모델링 패키지를 이용한 2D 축대칭(axis-symmetric) 유한요소 스트레스 모델링을 이용하여 검사되어 왔다.

스트레스와 변형은 극단적인 온도 증진에서 비아 제조 프로세스의 각 스테이지에서 평가되어야만 한다. 탄성 특성은 탄성률과 푸아송 비(Poisson ratio)를 특징으로 한다. 구리와 같은 일부 재료들의 경우, 재료의 항복강도(yield strength)가 초과되기 쉬워지고, 비선형 특성이 포함되어야만 한다. 응력-변형률 곡선(stress-strain curve)이 혼합될 수 있으나, 심플한 항복강도가 일반적으로 충분하다.

온도의 범위에 열팽창이 포함되어야만 함을 의미한다. 게다가 전단응력(shear stress)이 재질 인터페이스에서 평가되어야만 하고, 재질 간의 접합 강도가 비교되어야만 한다. 재질들이 프로세싱 동안 순차적으로 추가되었고, 각각의 프로세스 단계의 모든 레이어에 존재한 것은 아니다. 그러나 재질 레이어의 모두가 초기 유한요소 메싱에 포함된 경우에 모델링 프로세스는 단순화된다. 이는 존재한 레이어에 특정 힘이 가해지지 않도록 하기 위해서 제로 탄성율에 아직 증착되지 않은 재질 레이어를 제공함으로써 조정될 수 있다.

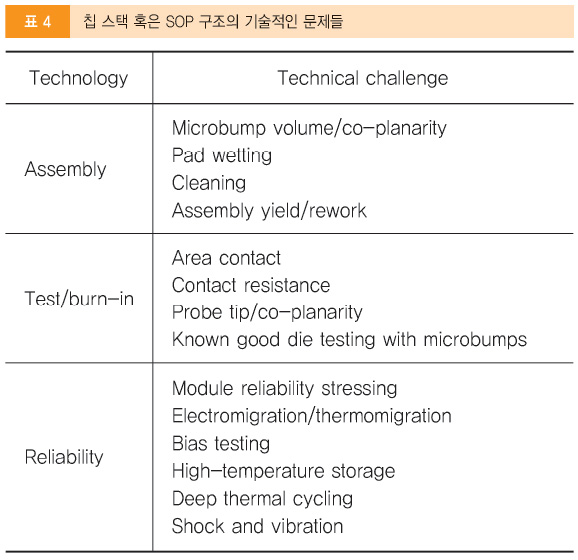

그림 12에서는 최대 온도와 실내 온도에서 50㎛×100㎛-deep 비아를 위해 완성된 비아의 상부에 first BEOL CVD 산화 레이어의 침전 후의 유한요소 셀에 상응하는 변형을 보여주고 있다. 변형은 더 잘 보이도록 10배로 확대되어 왔다.

가장 높은 응력 조건은 일반적으로 인접한 와이어링과 유전체층(dielectric layers)을 통해 보였다. 비아 구조와 프로세스 플로우의 기계적인 측면의 이해는 실리콘 기반 기술에 사용하기 위해 최대 수직적인 응력을 최소화하는 영향을 줄 수 있다. 구조 및 응력(예, 전자광학 트랜시버 혹은 실리콘 캐리어와 같은 칩 스택 혹은 SOP)의 이해에서부터 제품 애플리케이션을 위한 전기적 및 기계적 디자인 기준이 실리콘 관통-비아 기술을 이용하여 충족될 수 있다.

칩 스택 및 SOP 어셈블리, 테스트 및 모듈 신뢰성

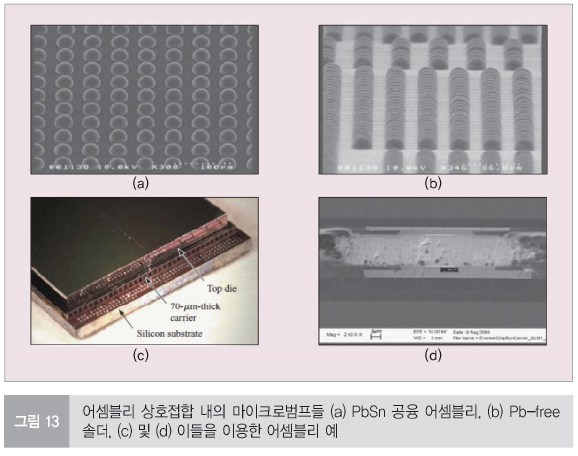

칩 스택 혹은 SOP 제품군의 중요한 요소는 테스트, 어셈블리 능력이고, 제품 애플리케이션을 위한 모듈 신뢰성을 보장하는 것이다. SOP 기술의 발달은 광범위하게 다양한 테스트 방법, 어셈블리 발달, 기술 증명 및 신뢰성 평가서를 포함해 왔다. SOP 기술을 활성화하는데 도움을 주는 역할을 하는 몇 가지 기술적 도전과 논증에 대해 설명한다. 칩 스택(예를 들면, 웨이퍼-레벨 프로세싱), 싱글-칩 및 멀티-칩 모듈을 포함한 다양한 애플리케이션을 지원하는 목표 연구가 설명되었다. Cu-본드(영구적인) 상호접촉의 칩 스택을 위한 모듈 신뢰성이 연구되었다. 이는 칩-투-실리콘 Cu 솔더(리웍 가능한) 상호접촉과 다르다. 그래서 구조, 상호접촉 및 애플리케이션, 어셈블리와 테스트에 의존하는 것은 필요한 제품 신뢰성을 지원해야만 한다. 어셈블리, 테스트 및 SOP 구조의 모듈 신뢰성을 위한 기술 도전은 표 4에 요약하였다. 기술적인 문제의 논의를 설명한다.

많은 요인들에 의존하는 어셈블리 방법론은 비용, 패키지된 칩 및 부품의 수, 어셈블리 수율 그리고 테스트 방법론을 포함하고 있다. 예를 들면, 패키지 상의 싱글 칩 혹은 패키지 상의 2개의 칩의 어셈블리는 웨이퍼 테스트 이후 및 테스트 비용을 최소화하는 방법론으로써 하는 전체 기능성 테스트 이전에 완성될 수도 있다. 복합 칩의 멀티칩 모듈의 경우, 각 칩은 어셈블리 이전에 기능성 테스트가 될 수 있다. 그런 후 멀티칩 모듈에 어셈블리된다. 과도한 어셈브리, 테스트 그리고 불량이 발생할 수 있거나 혹은 기능성 불량이 될 수 있는 특이한 사양의 칩과 전체 멀티칩 모듈의 리웍을 회피하기 위해서이다.

제조, 어셈블리, 테스트 및 신뢰성 연구의 경우, 4개 솔더 조성의 ㎛-C4 및 멀티플 BLM(ball-limiting metallurgies)가 평가되었다. 사용된 솔더 조성(wt.%)으로는 1) 납이 많이 포함된 솔더 (Pb/Sn; 97/3), 2) 공융 솔도(Pb/Sn; 37/63), 3) 납이 없는 Sn-Ag-Cu 계열의 합금(>95% Sn + 첨가제) 및 4) 납 없는 솔더(Au/Sn; 80/20)가 포함되었다. 100㎛ 및 50㎛ 피치에서 납 솔더의 사용은 Pb/Sn 97/3 및 Pb/Sn 36/63을 이용한 200㎛, 225㎛, 250㎛ 피치의 상호접합과 비교했을 때의 큰 데이터시트와 오랫동안의 직접적인 비교를 허용한다.

제조라인의 경우, ㎛-C4용 각 솔더 합금의 제조 능력은 선택 도금, IMS(injection-molded solder) 기술, 대체 제조프로세스를 이용하여 입증되어 오고 있다.

하드웨어 어셈블리는 칩-온-칩뿐만 아니라 하나 이상의 칩이 패키지 어셈블리에 사용되거나 솔더 배선 혹은 Cu-to-Cu 본딩을 이용한 웨어퍼-투-웨이퍼 레벨 프로세싱 어테치먼트로 이용되면서 입증되어 왔다. 초창기 연구에서는 50㎛ 피치 상의 25㎛ 마이크로범프와 100㎛ 피치 상의 50㎛ 마이크로범프를 이용하여 칩-투-Si-캐리어 어테치먼트가 가능한 다양한 테스트 제품들을 이용해 왔다. 공융, 무연, 고융점 및 AuSn 솔더가 테스트되었다. 공융 및 무연 솔더 어셈블리의 경우, 수 백 개의 접합부는 다이 당 I/O의 수가 2,160~10,000 이상의 범위에서 테스트 실험이 배선으로 실행되었다.

50㎛ 피치에서 5,200 마이크로범프를 지닌 다이를 대표적으로 촬영해 보면, 어셈블리는 100% 우수한 배선으로 완성하였다. 그림 13에서는 (a) Pb/Sn 공융, (b) 50㎛ 피치의 무연 솔더 뿐만 아니라 (c) 어셈블리된 칩, (d) 마이크로범프 종단면을 대표적인 마이크로범프를 보여주고 있다. 어셈블리 연구 및 이들 구조의 특성은 전기적, 기계적 및 신뢰성 응력을 이용하면서 유지되었다. 기계적 테스트의 예에는 칩 인장 테스트를 포함하고 있으며, 그림 11에서 보는 바와 같다.

50㎛ 피치와 100㎛ 피치 칩 마이크로범프 그리고 SOP 배선을 측정하는 전기 테스트 방법에는 예비 핸드 프로브, 고속 제조 프로브 및 에어리어 어레이 프로브 테스트를 이용한 조사를 포함하였다. 이른 핸드 프로브 이외에도, 새로운 테스트 칩과 테스트 구조의 입증은 고속 테스트 프로브 및 에어리어 어레이 웨이퍼-테스트 기술을 사용하여 IBM 제조 테스트에 이점을 가지고 있다.

고속 제조 테스트 프로브를 이용한 전기 테스트와 웨이퍼-테스트 방법론 입증은 지금까지 오픈과 쇼트 테스트를 위해 사용되어 왔다. 향상된 예에 따르면, IBM 내의 현재의 C4 접촉 프로빙 기술의 기본을 보고하였다. 그리고 그들을 칩과 이들 첨단 구조의 저-비용 웨이퍼 테스트 단계에 완전한 단계로 여겨져 왔던 새로운 프로브 기술이 테스트되었던 SOP 구조를 위한 ㎛-C4와 비교하였다.

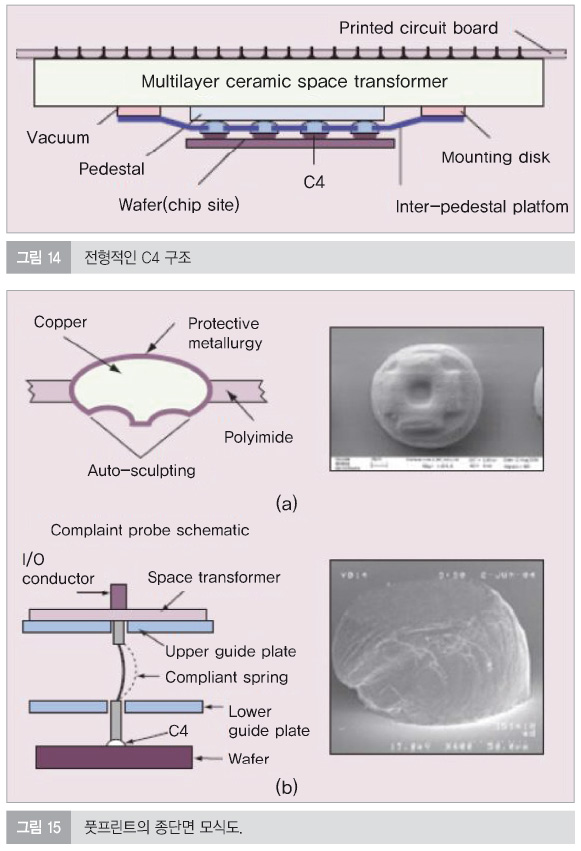

현재 웨이퍼 테스트에서는 그림 14에서 개략적인 종단면을 보여주는 바와 같이 TFI(thin-film interposer) 프로브가 200㎛ 피치 웨이퍼 내의 칩 테스트에 이용되고 있다. 프로브는 견고한 접촉을 제공하고, C4에 의존한다; 그림 15의 (a)는 TFI 프로브(좌)와 접촉 후 100㎛ 솔더볼로 접촉한 후의 좌측 풋프린트(우측)의 종단면 모식도이다. 이와 반대로, 그림 15의 (b) 좌측은 C4 컴플라이언스 요구가 아니라 C4 표면 상의 산화를 통해서 일부 표면 이동이 멈추는 것을 요구하는 컴플라이언스 Cobra 프로브의 대략도이다. 그림 15의 (b) 우측은 Cobra 테스트된 C4 솔더 범프를 보여주고 있다. 200㎛ 피치에서부터 파인-에어리어 50㎛ 피치까지 그리고 100㎛ 피치 웨이퍼 테스트로 현재의 기술을 확대하기 위해, 새로운 프로브 플랫폼이 정의되어 왔으며, 평가가 진행되고 있다.

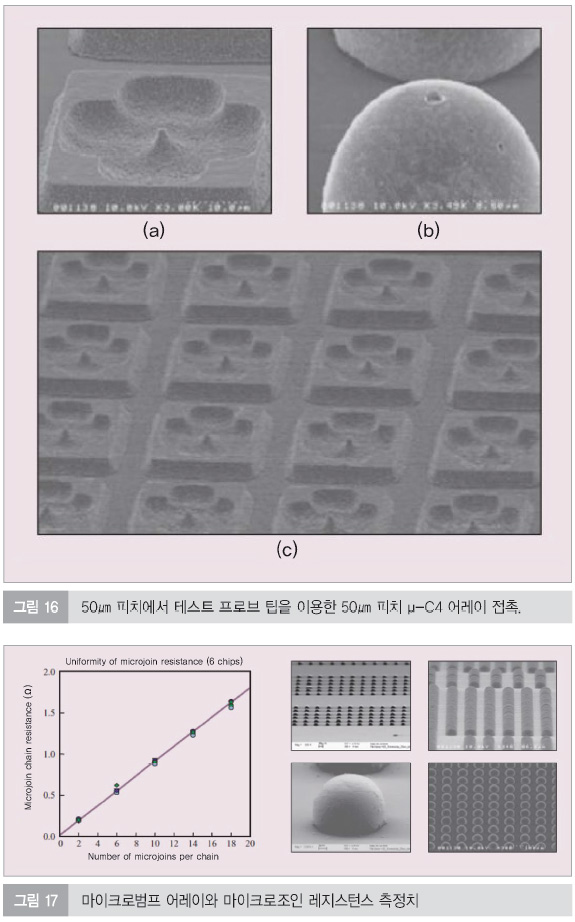

신규 웨이퍼-테스트 플랫폼은 에어리어 어레이 제조와 접촉이 에어리어 어레이 50㎛ 피치를 사용하여 입증된 프로브 팁 축소에 이용할 수 있다. 이 기술 방법이 50㎛ 이하로 잘 확대될 수 있다고 믿고 있다. 게다가, 백업-컴플라이언스 프로브 기술을 이용한 평가가 100㎛ 혹은 50㎛ 피치 혹은 그 이하에서 웨이퍼 테스트를 제공할 수 있는 기회를 주는데 정의되었다. 신규 에어리어 어레이 테스트 플랫폼의 조사 및 최적화화 에어리어 어레이 및 다이 테스팅용 프로브 팁이 유지하였다. 그림 16에서는 50㎛ 피치에서 테스트 프로브 팁을 이용한 초기 개발된 50㎛ 피치 μ-C4 어레이 접촉을 보여주고 있다.

초기 기본적인 전기 평가에는 전기 직류 접촉 저항, 패드 변형 및 신뢰할만한 접촉을 제공하는 능력이 포함되었다. 마이크로조인 체인의 전자동 4-포인트 저항 프로브 카드 테스트를 이용하여 일부 테스트 서브스트레이트의 직류 테스트가 실행되었다. 특히, 유용한 마이크로조인 체인 매크로에는 정밀하게 평가되고 플롯되도록 링크되어 체인의 성장 시퀀스의 평가를 가능하게 하는 테스트 디자인이 포함되었다. 개별적인 마이크로조인의 독립적인 3-포인트 평가뿐만 아니라 이들 체인을 이용하여, 50㎛ 직경 범프에 ~20㏁ 그리고 20㎛ 직경 범프에 ~50㏁의 저항 측정이 나타났다(그림 17 참조).

실리콘 관통-비아를 가진 실리콘 구조의 신뢰성 테스트, BEOL 프로세싱, μ-C4를 이용한 코플라나 전송선(coplanar waveguides) 빌트 및 모듈 구조는 정의되어 왔고 초창기 연구에서 시작되어 왔다. JEDEC과 호환 가능한 스트레스 테스트에는 -55℃~125℃까지의 DTC(deep-thermal-cycle) 스트레스 테스트, 온도 및 습도 비아 테스트, 전자이동 스트레스, 열 전송 스트레스, 고온 스토리지, 전력 사이클 및 쇼크 그리고 진동 테스트가 중점으로 포함되었다.

100㎛ 피치에 50㎛ 사이즈의 μ-C4 신뢰성 테스트에서는 -55℃~125℃의 1,000 DTC 그리고 0℃~100℃의 1,500 열사이클을 통과한 결과를 보였다. 전기 저항은 DTC 샘플에 3.5%~9.5%의 범위에서 증가된다고 측정되었다. 50㎛ 피치의 25㎛ 솔더 범프의 경우, 신뢰성 테스트 결과는 다음과 같이 나타났다: Non-underfilled 샘플들은 -50℃~125℃ DTC의 2,000 사이클에서 생존했다. 전자이동 테스트에서는 샘플들이 각각 2,000 시간의 경우 접촉당 62㎃ 그리고 920 시간 이상의 경우 접촉당 100㎃로 150℃의 온도에 생존했음을 보여주었다. 비아 전류 테스트를 이용한 온도 및 습도는 1.5V에서 언더필 없이 500시간을 생존했다.

신뢰성 스트레스 테스트에서의 전기, 기계적 및 물리적 분석 결과는 구조 증진과 이해하고 지속적으로 연구하는 테스트 방법을 증명하기 위해 사용되어 왔다.

마무리

차세대 SOP 기술은 새로 개발된 실리콘 관통 비아 컨덕터, 세미컨덕터 BEOL 멀티레벨 와이어링 그리고 애플리케이션 다양화를 위해 이 기술의 3차원 집적을 위한 파인-피치 I/O 상호접촉을 이용하여 IBM에서 지속적으로 연구하고 있다. 새로운 구조는 고속 상호접촉과 고대역 I/O 그리고 현재 산업계의 구조보다 10배 혹은 100배 이상으로 밀도가 높은 와이어링 밀도를 제공하기 위해 전기적으로 디자인되고, 모델화되었고 특징화되었다.

기계적인 모델링, 어셈블리, 테스트 및 신뢰성 연구는 이 새로운 기술이 이뤄질 수 있으며, SOP 애플리케이션의 보드 범위를 지지할 수도 있다고 지적되어 계속되었다.

반도체 진보를 위해 전기적, 열적 및 I/O 스케일링의 기술 로드맵 요구에 확대가능하게 한다. 지속적인 연구와 향상은 언급된 데이터베이스, 실리콘 패키지 제조, 테스트 및 어셈블리를 포함한 우수한 제조 프로세스를 정의하는데 도움을 줄 것이다. 또한 좀 더 효율적인 비용의 제품 공급을 보이는 제품 애플리케이션에 기술이 직접적으로 도움을 줄 것이다.

SOP 테크놀로지에서의 향후 작업에서는 실리콘 관통-비아 컨덕터의 평가, 구조의 전기적 특성, 광-전기 특성 그리고 기계적 및 신뢰성 평가를 포함할 것이다. 또한 향후 작업에서는 첨단 3-차원 구조를 위한 수동부품과 능동IC를 포함할 것이다. 새로운 2D 및 3D 구조를 사용하는 실리콘 및 패키징 집적은 지원 시스템 요구와 새로운 대량 생산 애플리케이션에 흥미를 유발하고 있다.